Enhance VLSI Timing Analysis Using Static Timing Analysis

2022/10/29 10:46:15

Views:

Within the world of Exceptionally Huge Scale Integration (VLSI) plan, exact timing examination plays a basic part in guaranteeing the usefulness, execution, and unwavering quality of coordinates circuits. As innovation scales and complexity increments, timing confirmation gets to be progressively challenging. A demonstrated strategy to handle these challenges is Inactive Timing Examination (STA), a effective procedure utilized to confirm timing in VLSI plans. This article dives into how STA moves forward VLSI timing examination, advertising bits of knowledge into its technique, applications, and benefits.

Op-Amps, Part 1: OpAmp LM324N Comparator

Table of Contents

- What is Static Timing Analysis?

- Key Concepts in Static Timing Analysis

- How STA Enhances VLSI Timing Analysis

- Static Timing Analysis in VLSI: An Example

- Real-time Clock Synchronization in VLSI Timing

- Challenges in Static Timing Analysis

- Static Timing Analysis Examples in the Industry

- Conclusion

- Commonly Asked Questions

What is Static Timing Analysis?

Static Timing Analysis (STA) could be a procedure utilized within the plan and verification of advanced circuits to foresee whether a plan will meet timing limitations without reenacting the whole circuit behavior. Instead of running dynamic simulations, STA checks all possible paths through a circuit to ensure signals arrive at the required points within specified time limits.

Unlike dynamic simulations that require input vectors, STA evaluates the timing characteristics of a circuit by calculating signal propagation delays across various paths. It ensures that signals do not violate setup and hold time requirements, providing a more efficient way of validating circuit timing than exhaustive simulation methods.

Key Concepts in Static Timing Analysis

Some time recently diving more profound into STA's affect on VLSI timing investigation, it's basic to get it a few center concepts related to STA.

Setup and Hold Times

One of the most targets of STA is to guarantee that setup and hold times are met. Setup time alludes to the least sum of time some time recently a clock edge that a information flag must be steady, whereas hold time is the sum of time after the clock edge that the flag must stay steady. Infringement in setup or hold time can cause failing of the circuit.

Clock Skew

Clock skew alludes to the contrast in timing between the clock signals coming to diverse parts of the circuit. Intemperate skew can lead to timing infringement, and STA is basic in distinguishing and relieving clock skew issues in VLSI plans.

Timing Paths

In any computerized plan, there are a few ways between the flip-flops and rationale doors that a flag may take. STA analyzes the timing of these ways to guarantee that the signals navigate inside the specified time limits, guaranteeing the plan works at the specified recurrence.

Timing Paths Example

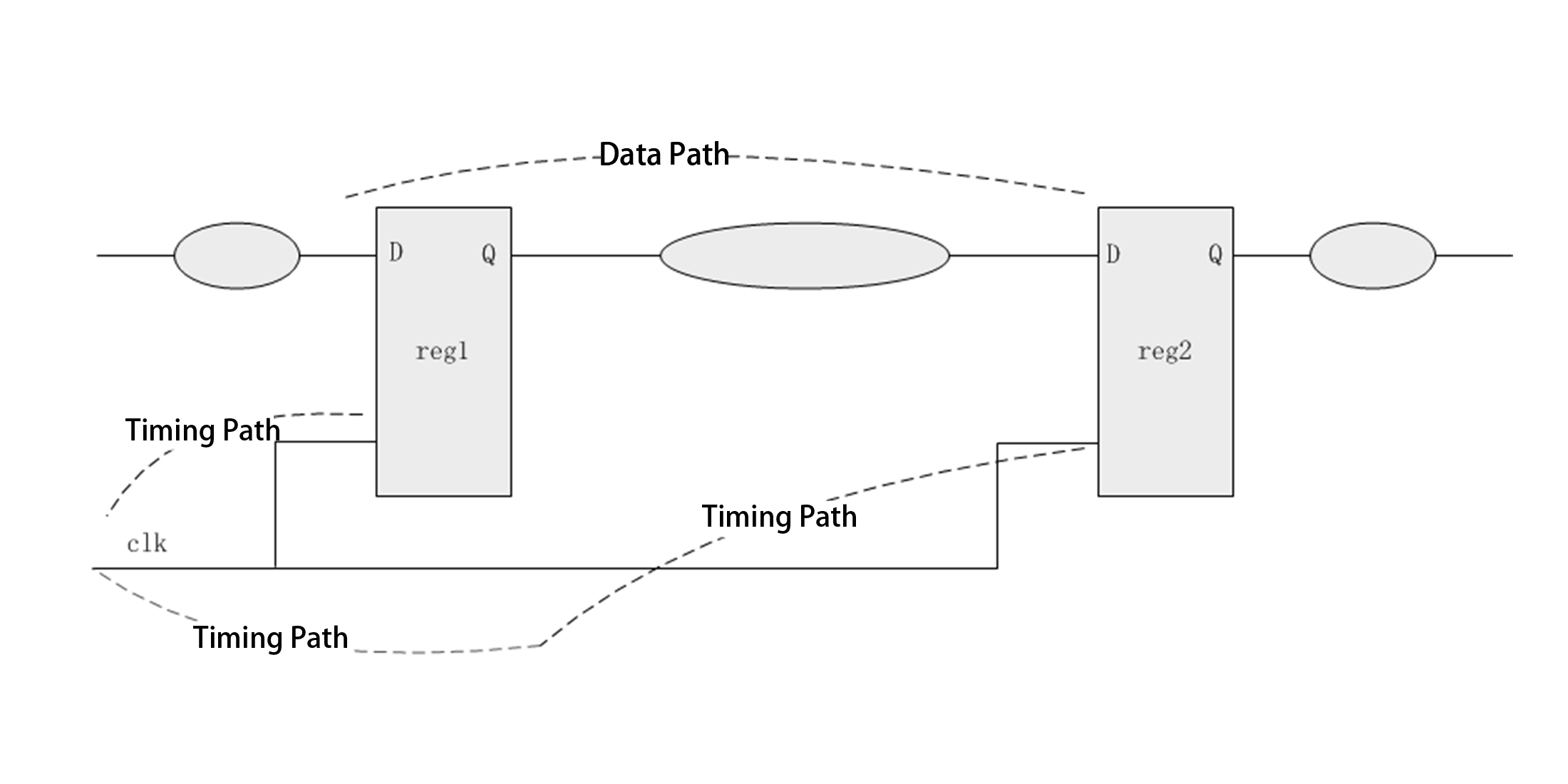

In the diagram below, you can see an example of a timing path between two registers (reg1 and reg2). The signal propagates from reg1 to reg2 through the combinational logic in the data path, while the timing path checks whether the signal meets setup and hold time requirements relative to the clock signal (clk).

Timing Concepts

How STA Enhances VLSI Timing Analysis

1. Comprehensive Coverage of All Paths

One of the most significant advantages of STA is that it analyzes all possible paths in the circuit, both the critical and non-critical ones. This comprehensive coverage ensures that no timing violation is overlooked, providing higher confidence in the design's performance. In contrast, dynamic simulation methods only analyze paths based on the provided input vectors, potentially missing critical timing violations.

2. Speed and Efficiency

STA is a faster and more efficient approach to timing analysis compared to dynamic simulations. Since STA doesn't require input vectors, it can quickly evaluate the circuit's timing characteristics without running multiple simulations. This speed is particularly beneficial for large-scale VLSI designs with millions of transistors.

3. Early Detection of Timing Violations

By utilizing STA timing early within the plan cycle, engineers can distinguish and settle potential timing infringement some time recently they gotten to be exorbitant and troublesome to resolve in afterward stages. Early discovery progresses the generally unwavering quality of the plan, diminishing the hazard of utilitarian disappointments.

4. Application to Multiple Clocks

Modern VLSI designs often involve complex clocking schemes with multiple clocks operating at different frequencies. STA is highly effective in analyzing timing paths involving multiple clocks and domains, identifying issues like clock skew and clock domain crossing violations.

5. Identifying Critical Paths

STA identifies critical paths in the design, which are the paths that dictate the maximum operating frequency of the circuit. By knowing which paths are critical, designers can optimize them to enhance the overall performance of the circuit. This optimization leads to faster designs, enabling higher clock frequencies and improved efficiency.

Advantages of STA

Static Timing Analysis in VLSI: An Example

To better understand STA's role in VLSI, consider the example of a digital circuit with combinational logic blocks connected between two flip-flops. The signals propagate from one flip-flop to another through the combinational logic, and STA evaluates the propagation delay across this path.

In this scenario, STA in VLSI ensures that the signal arrives at the destination flip-flop in time before the next clock edge, and it checks if the setup and hold times are met. If a timing violation is detected, STA can pinpoint the exact location and timing issue, allowing the designer to adjust the path or clock constraints accordingly.

Path Types and Impact

Real-time Clock Synchronization in VLSI Timing

Accurate clock synchronization is essential for high-performance digital systems. One crucial aspect of timing analysis of circuit performance is ensuring that multiple components and systems synchronize their clocks accurately. Modern systems use realtime analyzers to ensure precise time synchronization across the circuit.

Using NTP Synchronization

Network Time Protocol (NTP) is commonly used to synchronize clocks across distributed systems. NTP synchronize allows the system to maintain consistent timing across different components, ensuring no skew or delay in clock signals. This is particularly critical in VLSI designs that operate with high-speed communication protocols where precise timing is essential.

By employing sync network time, VLSI designers can mitigate the risks of clock domain crossing and timing violations that might arise due to asynchronous clocks. Clock NTP solutions ensure that all parts of the system are operating in sync, reducing the likelihood of timing errors.

Sync Clocks for Better Timing Accuracy

Synchronizing clocks across a circuit is essential for reliable data transfer and processing. Sync clocks can help ensure that all timing paths meet their requirements, especially in systems with multiple clock domains. STA works in tandem with clock synchronization techniques to enhance the timing reliability of VLSI designs.

Clock Synchronization Comparison

Challenges in Static Timing Analysis

Despite its numerous advantages, STA is not without challenges. Some of the common issues encountered during STA in VLSI timing analysis include:

1. Handling Multiple Clock Domains

Many VLSI designs have multiple clock domains that operate at different frequencies. Ensuring timing correctness across these domains can be challenging, as clock domain crossing introduces potential timing violations. STA helps mitigate these issues but requires careful design and clock synchronization strategies.

2. Modeling Process Variations

As process technologies shrink, the impact of process variations on timing becomes more pronounced. Variations in voltage, temperature, and fabrication processes can significantly affect timing behavior, and STA must account for these variations to provide accurate analysis results.

3. Accounting for Environmental Conditions

Timing behavior can change under different environmental conditions, such as temperature and voltage variations. STA must consider worst-case scenarios to ensure timing correctness in all operating conditions, which adds complexity to the analysis.

4. Non-Linear Behavior of Circuits

Some circuits exhibit non-linear behavior, which can be difficult for STA tools to model accurately. In such cases, designers may need to supplement STA with additional simulation methods to verify timing performance.

STA Challenges

Static Timing Analysis Examples in the Industry

STA is widely used in the semiconductor industry for the design and verification of various types of circuits, including microprocessors, digital signal processors (DSPs), and memory modules. Some common static timing analysis examples in real-world applications include:

Microprocessor Design: Ensuring that critical paths in the microprocessor meet timing requirements to achieve the desired clock frequency.

Memory Design: Verifying that read and write paths in memory modules meet setup and hold time constraints.

DSPs and GPUs: Checking timing across data paths and control signals to ensure high-performance computation.

Conclusion

Within the domain of VLSI plan, Static Timing Analysis is an vital instrument for guaranteeing that a circuit meets its timing necessities. By analyzing the timing ways, identifying potential infringement early, and optimizing basic ways, STA plays a vital part in moving forward the execution and unwavering quality of VLSI frameworks. In addition, the utilize of realtime analyzer devices, NTP synchronize conventions, and sync clocks instruments guarantees that timing remains exact over diverse spaces and components, enabling consistent operation of complex computerized circuits.

As innovation proceeds to advance, STA will stay a foundation of VLSI plan, making a difference engineers meet the ever-increasing requests for quicker, more solid, and more effective coordinates circuits. With headways in STA tools and techniques, long run of VLSI timing analysis looks shinning, advertising more exact and effective arrangements to the challenges of present day circuit plan.

Commonly Asked Questions

What is STA timing in VLSI?

STA checks signal paths in a circuit to ensure timing constraints are met without dynamic simulation.How does STA improve VLSI reliability?

STA detects timing issues early, preventing circuit failures and ensuring stable operation.Why is STA faster than dynamic simulation?

STA doesn't need input vectors, analyzing all paths directly, making it quicker.What is clock skew in STA?

Clock skew is the timing difference between clock signals; STA helps minimize it to prevent violations.Why are setup and hold times important in STA?

They ensure signals are stable before and after the clock edge, preventing malfunction.Related Information

-

-

Phone

+86 135 3401 3447 -

Whatsapp